位密度,将生产率提高了约20%”[1]。TechInsights在2023年2月17日发布的三星Galaxy S23 plus5X DRAM器件[2]。经过深入的SEM和TEM成像,并结合TEM EDS/EELS元素分析,TechInsights即将发布三星D1a nm 16 Gb LPDDR5X器件的分析报告。基于结构和材料逆向工程分析数据,TechInsights发现了四种EUV光刻(EUVL)工艺,用于阵列有源切割/外围有源(有源修剪)、位线接触(BLC)、存储节点接触垫(SNLP)/外围第一金属层 (M1)和存储节点(SN)管图形化。通过逆向工程分析没有明显的证据来确定EUVL工艺的第五层图形化层。

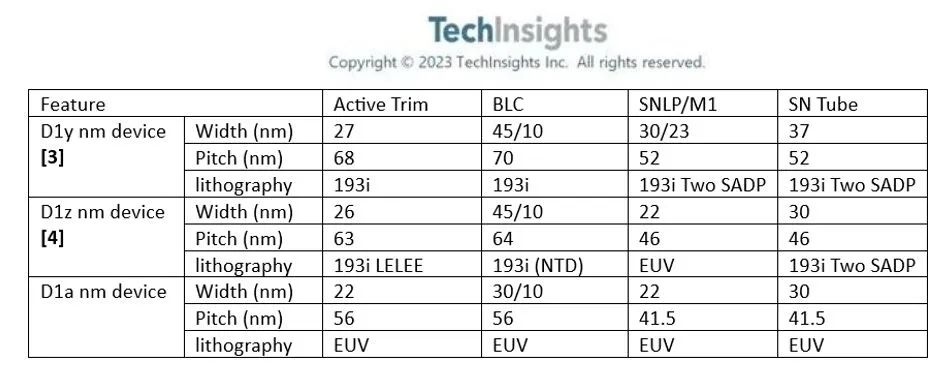

下表列出了三星D1y nm、D1z nm和D1a nm工艺器件的阵列有源切割、BLC、SNLP、SN管的最小宽度和节距,以及用于每层制模的光刻工艺。

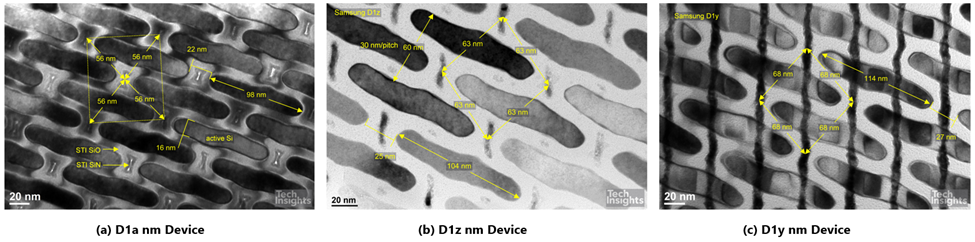

下图包含了三星D1a nm(图a)、D1z nm(图b)和D1y nm(图c)器件在存储阵列有源层的TEM平面视图。存储器阵列中的有源切口具有交错孔布局。三星D1y nm器件的阵列有源切割间距为68 nm,达到了193i光刻的分辨率极限。单193i光刻工艺用于图形化阵列有源切割/外围有源。三星D1z nm器件的阵列有源切割间距为63 nm。双图形化工艺可能用于图形阵列有源切割/外围有源。三星D1a nm器件的阵列有源切割间距为56 nm。

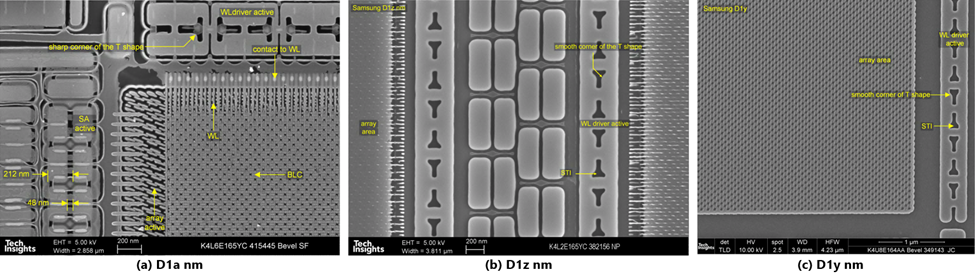

图2是三星D1a nm (a)、D1z nm (b)和D1z nm (c)器件在外围有源层的SEM平面视图图像。WL有源驱动中间的T型STI有一个尖角,如图2(a)所示;而WL有源驱动中间的T型STI有一个相对光滑的角,如图2(b)和图2(c)所示。这清楚地表明,存储阵列中的有源切口和外围的有源切口采用的是单一EUVL工艺,而不是193i双重图形化工艺。

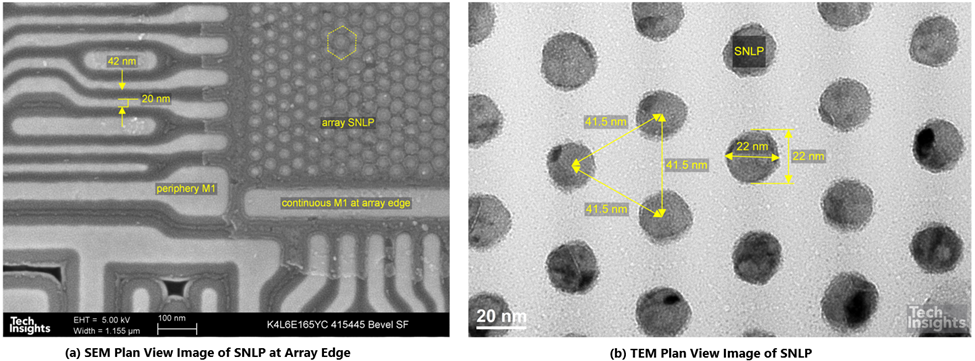

图4包括了三星D1a nm器件SNLP层的SEM (a)和TEM (b)平面视图图像。与三星D1z nm制程器件相同,圆形SNLP和阵列边缘的连续M1线表明使用单个EUVL制程对存储节点接触垫(SNLP)和外围M1进行了图形化。

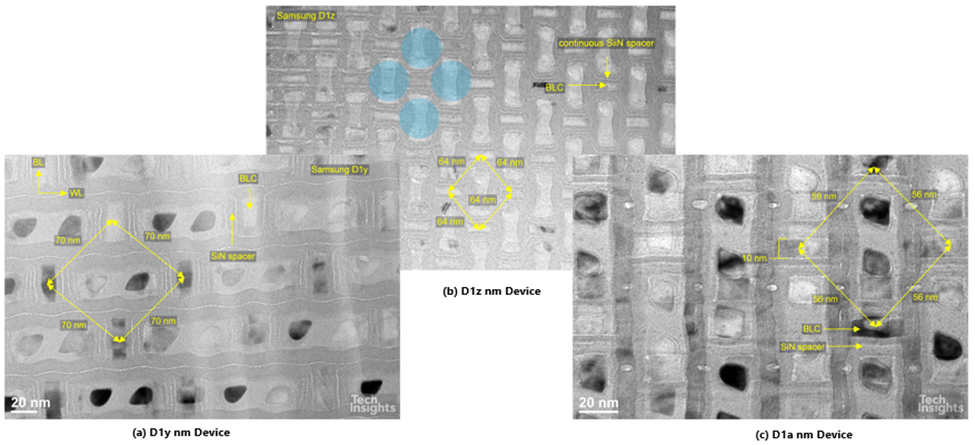

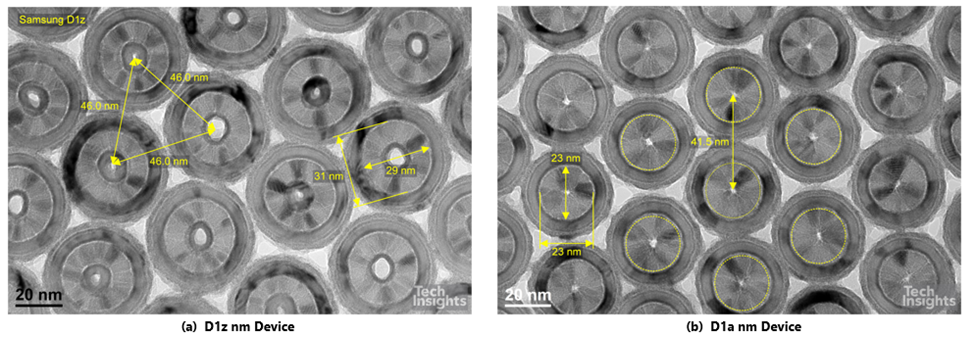

图5为三星D1z nm (a)和D1a nm (b)器件电容层的TEM平面视图图像。D1z nm器件的电容存储节点(SN)管间距为46.0 nm, D1a nm器件的SN管间距为41.5 nm。在三星D1z器件中,采用双向自对准双图像化工艺对SN管进行图像化(详见三星12Gb 1z EUV LPDDR5 process Flow Full, PFF-2102-801)。如图5 (a)所示,由于双向自对准图像化工艺的偏移和工艺均匀性问题,部分SN管在一个方向上比另一个方向略微拉长。D1a nm器件中的SN管在TEM斜角水平呈圆形,直径为23 nm(图5 (b))。因此,单一EUVL工艺可能用于三星D1a nm器件的SN管图案。

的基本步骤 ***的整体结构图 /

讲解 /

详解 /

步骤,耗时长、成本高。半导体芯片生产的难点和关键点在于将电路图从掩模上转移至硅片上,这一过程通过

的基本原理 /

详细流程图 /

IP 现已支持客户使用,该 IP 采用全新高性能、可扩展的自适应架构,并依托于 Cadence 久经验证且大获成功的

【米尔-全志T113-i开发板试用】移植libmodbus库到米尔-全志T113-i开发板