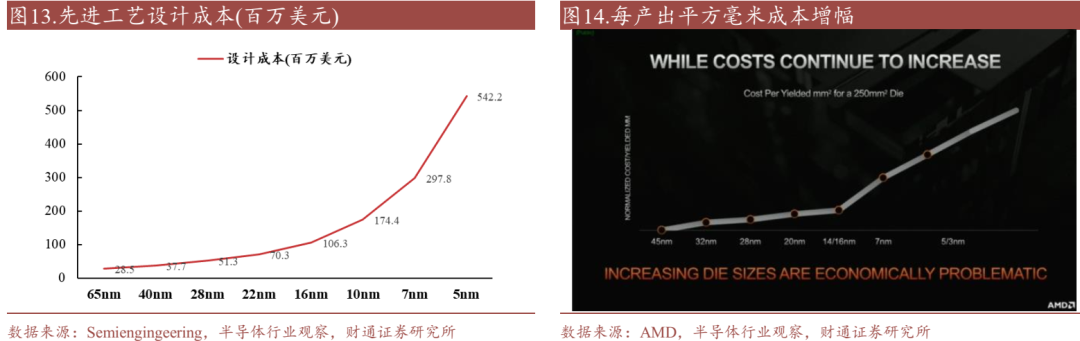

摩尔定律迭代减缓,5nm以下先进制程开发难度及成本难度提升。长期以来,芯片制程微缩技术一直驱动着摩尔定律的延续。从1987年的1um制程到2015年的14nm制程,芯片制程迭代速度一直遵循摩尔定律的规律,即芯片上可以容纳的晶体管数目在大约每经过18个月到24个月便会增加一倍。但2015年以后,芯片制程的发展速度进入了瓶颈期,7nm、5nm制程的芯片量产进度均落后于预期。全球领先的晶圆代工厂台积电3nm制程芯片量产遇阻,2nm制程芯片的量产更是排到了2024年后,芯片制程工艺已接近物理尺寸的极限1nm,芯片产业迈入了后摩尔时代。根据Semiengingeering统计的数据显示,16nm节点需要1亿美元,7nm节点需要2.97亿美元,到了5nm节点,开发芯片的费用将达到5.42亿美元,3nm研发费用或将超过10亿美元。,AMD的研究图表也显示,相较于从45nm发展到16nm的过程,从16nm发展到7nm和5nm所带来的成本增幅明显更高。

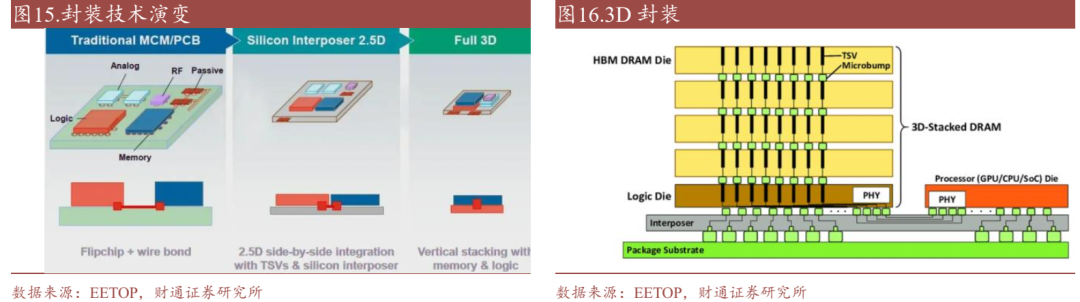

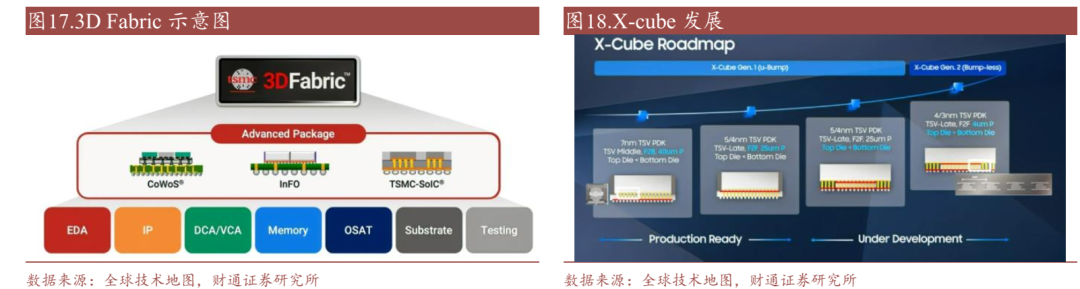

摩尔定律逐步到达极限,随着芯片产业的高速发展,芯片之间的数据交换呈现出倍数增长,传统的芯片封装方式已经无法满足如此巨大的数据处理需求,先进封装的重要性日益凸显。封装技术的发展经历了五个阶段,原件插装、表面贴装、面积阵列封装、异质整合、2.5/3D堆叠。2.5D封装是一种高级的异构芯片封装技术,可将多个芯片集成到一个封装中,并通过高密度线路连接。在这种封装中,多个芯片平行放置在中介层的顶部,通过微凸块和中介层的布线进行连接。中介层是由硅和有机材料制成的硅基板,其中的硅通孔(TSV)将上下层连接起来,同时通过锡球焊接到传统2D封装基板上,形成多芯片模块传递电信号的通道。中介层扮演着多芯片和电路板之间的桥梁角色,可实现芯片间和芯片与封装基板之间的互连。3D堆叠技术的特点是将多个芯片在垂直方向上进行封装,即在不改变封装体尺寸的前提下,将两个或更多芯片在封装体内进行垂直方向的叠放,主要包括倒装芯片(Flip Chip)和硅通孔(TSV)等技术。三星在2020年8月公布了“X-cube”技术,该技术采用TSV技术实现芯片间垂直互联。通过缩短芯片之间的信号距离,该技术能够提高数据传输速度并降低功耗。台积电在2022年10月宣布成立3D Fabric联盟,以协助客户快速实现芯片级创新迭代,采用3D硅堆叠先进封装技术来提高芯片性能。相比传统封装技术,先进封装的优势在于其能够优化连接方式并实现更高密度的集成,同时更容易实现异构集成。

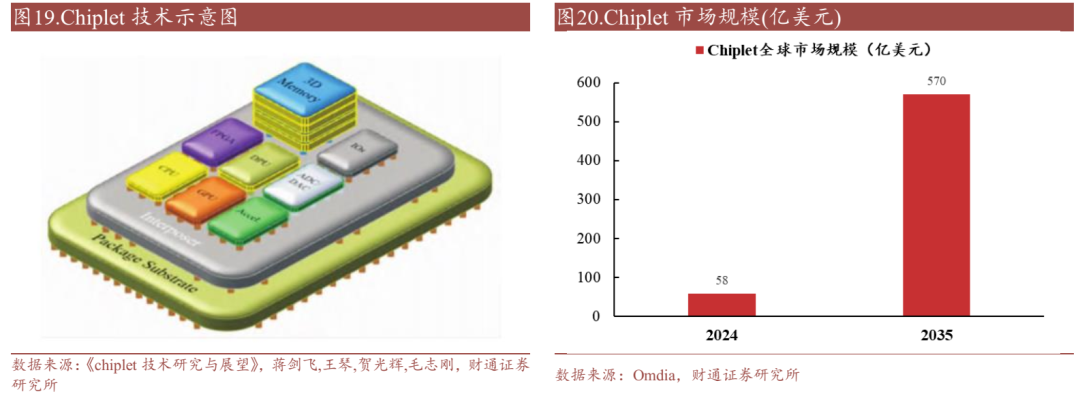

Chiplet或成为我国半导体行业突破美国封锁,实现弯道超车的新方式。Chiplet技术指的是将一个芯片分割成多个小芯片,并采用先进的封装技术重新组合成一个完整的系统。这种技术提高了不同部件之间的协同效应,提高了传输速度和效率。此外,在裸芯缺陷率相同的情况下,分割成小芯片后的面积更小,剔除的部分也更少,整体良率更高,因此Chiplet技术可以有效提高芯片的良率并降低成本,同时,IP能够快速复用,大大降低成本,促进产品迭代。据Omdia数据显示,2024年Chiplet市场规模将达到58亿美元,2035年Chiplet市场规模将达到570亿美元,有望拉动先进封装材料发展。

集成电路封装材料作为先进封装中必不可少的原材料。据Yole的数据显示,2020年全球先进封装市场规模约为304亿美元,占据封测市场的45%。据Yole的数据显示,预计在2021-2027年,全球先进封装市场规模将以9.66%的年均复合增长率增长,并在2027年达到650亿美元。虽然中国先进封装市场份额仍较低,但是仍具有广阔的产业升级空间。根据华经产业研究院的数据显示,2021年中国先进封装市场规模约为399.6亿人民币,同比增长13.7%,占据全球市场规模的15.7%。未来,先进封装工艺将成为封测行业增长的新动力。据国际半导体设备与材料产业协会(SEMI)的数据,2022年全球半导体材料市场总规模为692亿美元,较2021年增长7.62%。其中,晶圆制造业材料市场的销售额约为451亿美元,占据材料市场总规模的65.17%;而封装业材料市场的销售额约为241亿美元,占据材料市场总规模的34.83%。

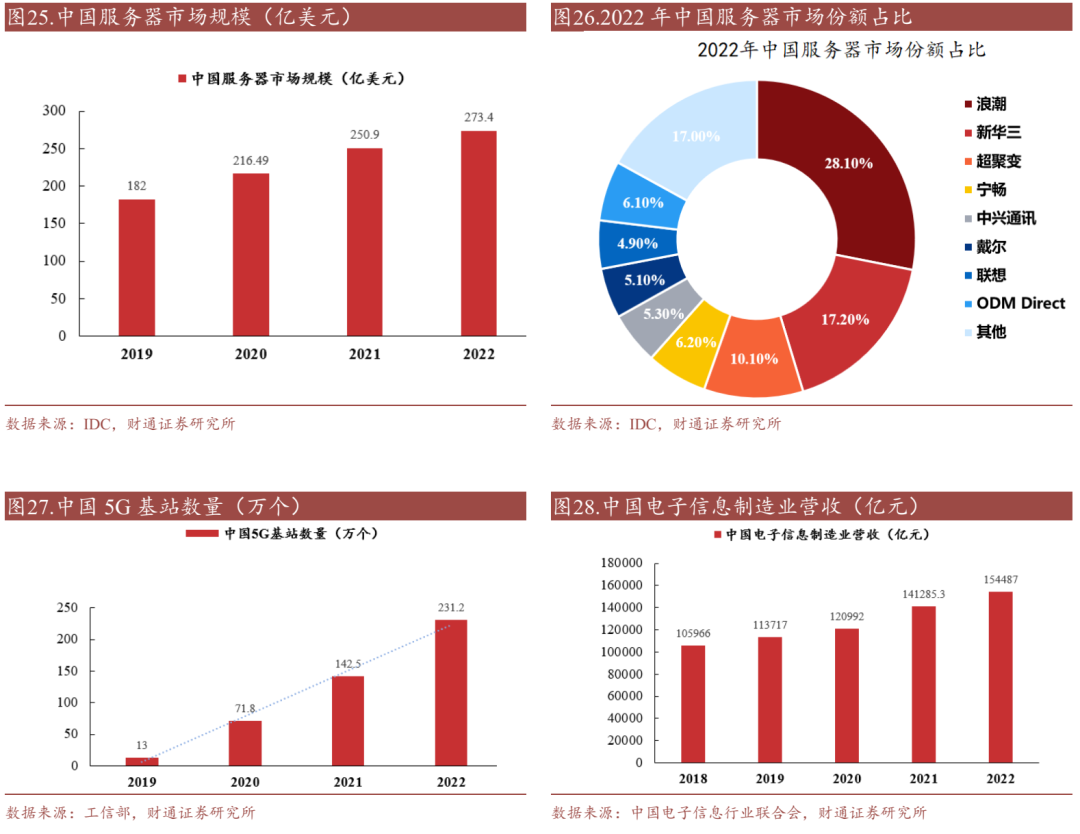

下游应用领域需求增长,带动封装材料市场发展。近年来随着科技下游尤其是移动互联网、网络通信、消费电子等发展,封装材料需求持续上升。在服务器领域,IDC发布的《2022年中国服务器市场跟踪报告》显示,2022年中国服务器市场规模为273.4亿美元,同比增长9.0%。网络通讯领域,2022年我国5G****总建设数新增88.7万个,达到231.2万个。消费电子方面,2022年我国规模以上电子信息制造业营收154487亿元,同比增长5.5%。下游应用领域快速增长带动上游封装材料尤其是国产集成电路封装材料出货量的增长。

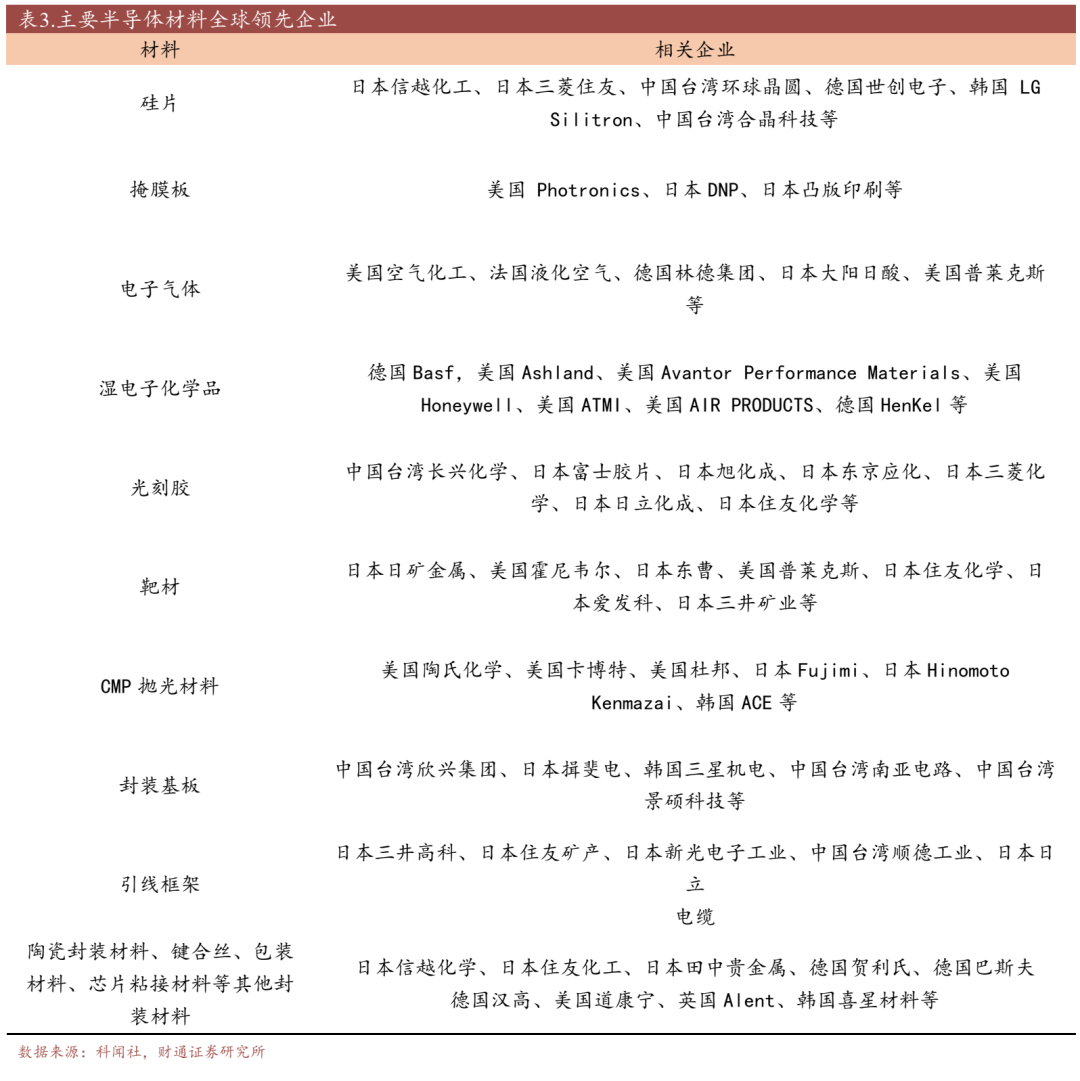

半导体材料领域国产化程度低,几乎被国外垄断,亟待国产替代。半导体材料包括晶圆制造材料和封装材料,其中晶圆制造材料包括硅片及硅基材料、光掩膜板、电子气体、光刻胶、光刻胶辅助材料、CMP抛光材料、工艺化学品、靶材等;封装材料包括封装基板、引线框架、键合丝、包装材料、陶瓷基板、芯片粘接材料等。长期以来半导体材料被国外垄断,据VLSI数据,近十年前十大供应商市场份额总和在50%左右,部分细分品类市场集中度达80%以上,被国外厂商垄断,国产材料崛起、替代空间巨大。当前,在全球消费电子、新能源汽车、通信设备等产业产能加速向中国转移的背景下,从产品交期、供应链保障、成本管控及技术支持等多方面考虑,原材料国产化的需求十分强烈,国内高端电子封装与新能源材料企业迎来了重大的发展机遇。

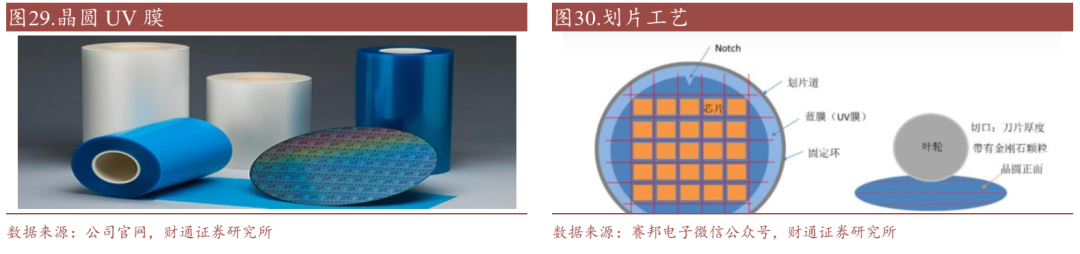

晶圆级封装材料主要是晶圆UV膜,包括晶圆UV减薄膜、晶圆UV划片膜。晶圆UV 膜是用于半导体制造前道工序中切割、划片的关键材料之一,产品性能直接影响晶圆加工的良率。该材料主要用于辅助保护TSV/3D晶圆减薄工艺中的晶圆,包括粘接、保护和捡取等。这种材料需要具备机械性能平衡性、稳定性和可靠性,以适应晶圆生产工艺的高精度和大批量生产的需求,同时还需要能够在高湿度和震动等特殊工作环境中工作。

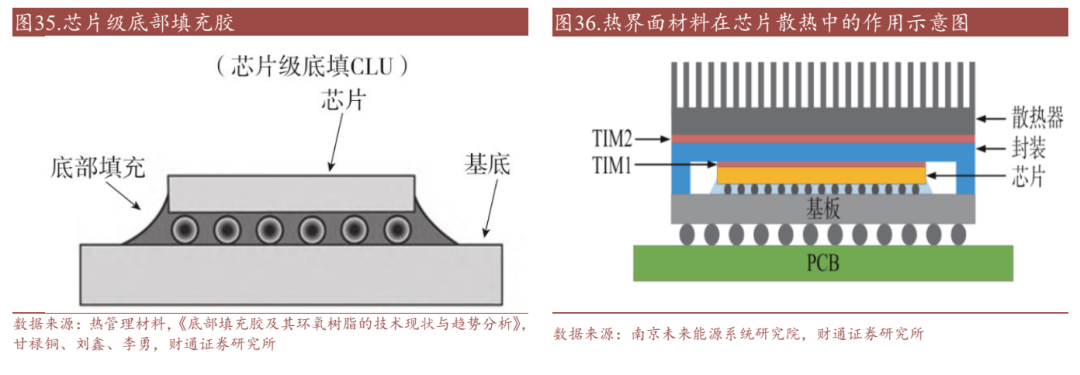

芯片级封装材料主要包括芯片固晶材料、芯片级底部填充胶、Lid框粘接材料。芯片固晶材料、芯片级底部填充胶是芯片封装工艺中起到粘接、固定或倒装封装保护等作用的关键材料之一,产品性能直接影响芯片封装的良率。其中,芯片固晶材料包括芯片固晶导电胶、绝缘胶、固晶膜等,主要用于芯片封装过程中的固晶工艺。这个工艺对于粘接材料的要求很高,需要具备低挥发、无气孔、高导电、高导热、高抗湿气性、低操作难度等特点。芯片级底部填充胶用于芯片和基板之间的连接。它可以分散芯片表面的应力,并缓解芯片、焊料和基板三者热膨胀系数不匹配产生的内应力,保护焊球并提高芯片的抗跌落和热循环可靠性。为了实现这一目的,产品需要具有良好的流动性、高可靠性和低热膨胀系数,需要采用高配方和精细工艺。Lid框粘接材料主要用于连接芯片基板和Lid框,其主要难点在于确保产品可靠性、厚度均匀、粘接性以及与不同封装尺寸的匹配性。

板级封装材料包括板级底部填充胶、板级封装用导热垫片。主要用于手机、电脑、平板等终端产品中PCB 板级封装工艺中起到结构粘接、导热、导电等用的关键材料,产品性能直接影响集成电路板级封装的良率。具体的,在内部印制电路板(PCB)封装工艺中,板级底部填充胶被用于填充芯片与电路板之间的空隙,以实现芯片的密封与保护,并在高温、高湿的环境下保持稳定的机械强度和粘接强度。板级封装用导热垫片,是在集成电路封装工艺中为了芯片散热而使用的,具备出色的导热特性,以及低密度和压缩比优异等特点。